# Wideband Dual-Injection Path Self-Interference Cancellation Architecture for Full-Duplex Transceivers

Tong Zhang<sup>®</sup>, Member, IEEE, Chenxin Su, Student Member, IEEE, Ali Najafi, Student Member, IEEE, and Jacques Christophe Rudell, Senior Member, IEEE

Abstract—A transceiver front end including a dual-injection path self-interference (SI) cancellation architecture is proposed for use in wideband full-duplex networks. The SI cancellation circuitry is implemented using: 1) one feedforward cancellation path containing a five-tap analog adaptive finite-impulse response (FIR) filter between the transmitter (TX) output and the receiver (RX) input; 2) a second baseband (BB) cancellation path containing a 14-tap low-frequency FIR filter with a point of injection at the RX BB output; 3) a phase noise cancellation method that suppresses the reciprocal mixing products associated with the downconversion in the BB cancellation path for the TX SI signal; and 4) an integrated noise cancelling power amplifier (PA). A prototype of 40-nm TSMC device was fabricated, which demonstrates more than 50-dB SI cancellation over 42-MHz bandwidth and a 10-dB attenuation of TX SI phase noise in the RX signal path. The two cancelling filters dissipate 11.5 mW, with a measured  $P_{-1\,\mathrm{dB}}$  and IIP<sub>3</sub> of 27/26.5 and 36/34.5 dBm, respectively. The RX noise figure is degraded by less than 1.55 dB, when both cancellers are enabled. The PA has a measured output of  $P_{-1 \text{ dB}}/P_{\text{sat}}$  of 25.1/26.5 dBm, respectively. The total chip die area is 3.5 mm<sup>2</sup> with an overall transceiver power consumption of 49 mW, excluding the integrated PA.

Index Terms—Adaptive finite-impulse response (FIR) filters, CMOS integrated circuits, delay lines, fifth generation (5G) mobile communication, interference cancellation, radio frequency, radio spectrum management.

#### I. INTRODUCTION

THE demands for higher wireless data rates continue to remain strong with some estimates projecting a factor of 5–10× increase in the upcoming years. This is driven by applications, such as video delivery to mobile smartphones, cloud computing, and the Internet-of-Things (IoT) [1]–[4]. However, all of the spectra below 6 GHz are allocated to the existing standards and applications, such as ZigBee, GPS, cellular phones, and Wi-Fi networks, in addition to frequency allocations dedicated to government functions including police, fire, and military communication. Full-duplex (FD)

Manuscript received September 7, 2017; revised January 8, 2018; accepted January 31, 2018. Date of publication March 6, 2018; date of current version May 24, 2018. This paper was approved by Associate Editor Pietro Andreani. This work was supported in part by NSF under Grant 1408575, in part by Google Inc., in part by Qualcomm, in part by Marvell Tech., and in part by CDADIC. (Corresponding author: Tong Zhang.)

The authors are with the Department of Electrical Engineering, University of Washington, Seattle, WA 98195 USA (e-mail: togzhang@uw.edu; suc4@uw.edu; anajafi@uw.edu; jcrudell@uw.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2018.2805874

communication presents an opportunity to increase spectral efficiency by allowing a single radio's transmitter (TX) and receiver (RX) to simultaneously operate using one carrier frequency (on the same channel) [5]–[19], for better usage of the existing commercial radio spectrum and effectively increasing the capacity of the existing wireless networks.

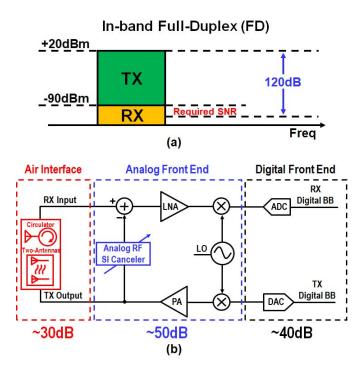

Although FD communication will potentially increase spectral efficiency by as much as 2× when compared to the existing frequency division duplex (FDD) systems, significant engineering challenges, which includes the cancellation of the TX self-interference (SI) signal present at the RX frontend [5]–[7], [20]–[34], exist. The large difference between the maximum TX power and the minimum required RX sensitivity demands a method to attenuate the signal power of the strong TX SI signal, which is particularly true in high-performance applications such as Wi-Fi, cellular, and evolving fifth generation (5G) wireless standards. As an example, some flavors of Wi-Fi transmit up to +20 dBm output power, while the RX sensitivity is as low as -90 dBm. Depending on the modulation method, more than 120 dB SI cancellation may be required [Fig. 1(a)].

To achieve a high SI cancellation (~120 dB) compatible with longer range radios that require a high output power TX, the function of SI cancellation should be distributed along the RX chain. For example, using an air interface that is realized with either a single antenna and a circulator, or two antennas, and assuming that these components provide a TX–RX isolation up to 30 dB, and further assuming that a 40 dB cancellation is provided by the digital backend, this leaves approximately 50 dB of cancellation for the analog/RF front end to achieve [see Fig. 1(b)] [23].

An ideal SI canceller should contribute minimal noise to the RX front end, occupies minimal silicon area, and has minimal added power consumption [35]. There have been numerous recent efforts to perform on-chip SI cancellation in the analog/RF front end. These cancellation techniques can be categorized as either passive [35]–[47] or active methods [21]–[24], [31], [48]–[57]. However, these methods often occupy significant silicon die area [35]–[47] or provide insufficient canceller linearity performance, which limits the maximum TX output power [21]–[24], [31], [48]–[57]. Moreover, both the depth and bandwidth (BW) of the cancellation are insufficient for applications that operate on a wide BW (>40 MHz), multi-carrier, high-output power amplifier (PA)

Fig. 1. SI cancellation in FD communication. (a) SI cancellation requirement in an FD radio with a TX output power of 20 dBm and a RX-required sensitivity of -90 dBm. (b) SI cancellation distributed in the RX chain.

signal, as is the case with evolving 5G wireless standards. Thus, the focus of the FD front end described in this paper is on the realization of a cancellation network that operates on a broad channel BW (40 MHz), with deep SI attenuation (50 dB+) as well as high linearity to allow the integration of high-output power PA ( $P_{\text{sat}} = 25 \text{ dBm}$  and  $P_{\text{max}} = 15 \text{ dBm}$  in the FD mode).

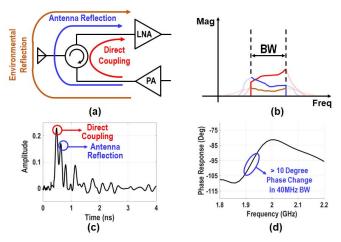

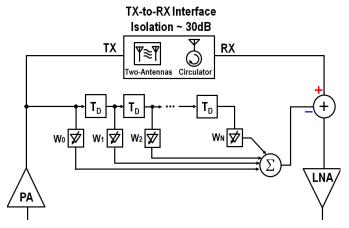

The design of a high-performance wideband SI canceller is challenging due to the fact that there are multiple time delayed paths of the SI signal over the channel BW of interest. A transceiver front end with a circulator and a single TX/RX shared antenna is used to illustrate this concept [Fig. 2(a)]. The SI is a combination of several leakage paths that include: 1) a direct-coupling path through the circulator, chip, and board substrate; 2) reflection from the antenna due to the imperfect matching between the antenna and the RX; and 3) a combination of other environmental reflections from nearby objects (e.g., human ear and metal objects). Each of the SI leakage paths will have a different frequency response and transfer function [Fig. 2(b)]. If it is assumed that each leakage path is linear time-invariant (LTI), then the overall leakage channel response can be modeled as a combination of the frequency response associated with each leakage path. To better understand the existence of multiple time-delayed coupling paths between the TX and the RX, measurements were made of a commonly found discrete circulator (Meca Electronics #CS-1.950) using a network analyzer and the results of which are shown in Fig. 2(c) and (d). This indoor measurement was taken with the antenna port of the circulator terminated using a 50- $\Omega$  load impedance. A two-port

Fig. 2. Channel response of the leakage path. (a) Multiple time delay paths of the leakage signal coupled from PA output to LNA input. (b) Conceptual frequency response for each time delay versions of the leakage signal. (c) Impulse response of a discrete circulator from Meca Electronics. (d) Phase response of the measured discrete circulator.

short-open-load-through (SOLT) calibration is performed on the TX and RX ports before taking the actual circulator measurement. It is worth mentioning that the measured circulator response is different from the actual leakage channel response. The leakage channel response is complicated and should take into account some secondary effects such as the response of the cable and package. The measured phase response of the circulator from the TX to the RX port shows a significant change (10°) over a BW of 40 MHz due to the multiple time-delayed coupling paths [see Fig. 2(d)]. As such, to realize a wideband suppression of the TX-to-RX SI, the canceller must provide an inverse channel response of all the summed leakage paths.

Several recent research efforts attempt to achieve wideband and high SI cancellation using a single feed-forward path [21] or a single point of injection [51]. In [21], a secondorder  $G_m$ -C N-path filter was used to perform frequency domain equalization. However, a high-frequency multiphase clock network must be distributed to a set of switches, which will likely dissipate considerable power. An alternative method synthesizes an inverse leakage signal at the LNA input using a current DAC and upconversion mixer [51]. However, for applications requiring a high RX sensitivity, the DAC quantization noise will potentially degrade the RX sensitivity. Thus, it is challenging to achieve sufficient SI suppression using a single feedforward path for a wideband TX signal, in situations where a high-power PA operates simultaneously with a high-sensitivity RX. Moreover, the cancellation DAC lacks the ability to capture the broadband noise and nonlinearities produced by the TX. While examples do exist of a single-circuit block achieving TX SI cancellation of greater than 50 dB [39] for narrowband applications, generally achieving this level of suppression/cancellation for a wideband signal remains difficult. Examples might include single-sideband mixers [58], filters, and harmonic rejection mixers [59], [60].

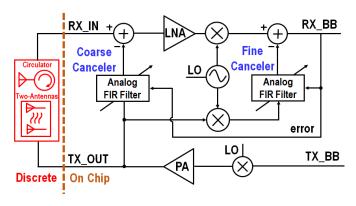

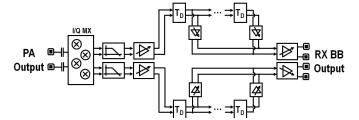

Fig. 3. Proposed dual-injection path SI cancelling architecture.

The remainder of this paper explores an SI cancelling architecture that overcomes those aforementioned challenges by performing SI cancellation at multiple points in the RX. This is followed by an expanded description of the prototype chip, which was first given in [20].

#### II. DUAL-INJECTION PATH FULL DUPLEX ARCHITECTURE

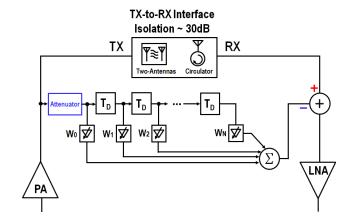

This transceiver makes use of a dual-injection path SI cancelling architecture that allows more design freedom to achieve both a deeper attenuation of TX leakage over a broader BW (see Fig. 3). Two analog cancellers, both of which have their inputs attached to the TX output matching network, are designed to properly capture not only the TX carrier signal, but also the noise and non-linear distortion introduced by the TX.

The first RF canceller resides between the PA output and the RX LNA input, with the primary function of reducing the TX SI power sufficiently to prevent the RX front end from saturating. This has the effect of relaxing the required linearity for the LNA and all the subsequent RX blocks. The second baseband (BB) canceller benefits from the RX gain (30 dB), and thus, the RX is more forgiving of a noisy feedforward injection path as compared to a canceller with an output that feeds the RX input. This allows the realization of a significantly lower frequency, complex I/Q 14-tap analog finite-impulse response FIR filter. The BB canceller has an added advantage of capturing and cancelling the TX leakage reciprocal mixing with the LO phase noise in the RX signal path. The combination of both cancelling filters, with their outputs injected at different points in the RX chain, provides a wideband and high SI cancellation. More details covering the design of this dual-injection point cancelling architecture are discussed in Section III.

# III. DUAL-INJECTION PATH CANCELLER DESIGN CONSIDERATIONS

Several practical design issues are associated with this FD architecture, which include: 1) system-level design tradeoffs between the cancellation BW and the noise performance; 2) canceller design techniques to improve the linearity; and 3) cancellation of the TX SI signal reciprocal mixing with the LO phase noise in the second BB cancellation path.

Fig. 4. RF canceller (analog FIR filter) block diagram.

#### A. First Coarse RF Canceller

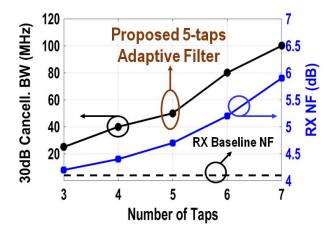

The RF cancellation path is implemented with an analog adaptive FIR filter using true-time delay blocks for the delay elements and transconductance stages to realize the filter taps [61] (Fig. 4). A similar approach to an RF feedforward canceller was demonstrated in the discrete form at Sigcomm [5]. As mentioned earlier, the RF canceller is designed to attenuate the TX SI signal significantly, thus relaxing the linearity requirements of the entire RX. However, there exist design tradeoffs between the number of filter taps used by the feedforward canceller, the degradation in the RX noise figure due to the noise generated by the canceller path, and the cancellation bandwidth (BW). To better understand these tradeoffs, a set of simulations were performed with both MATLAB Simulink (cancellation BW simulation) and Cadence SpectreRF (noise simulation); results are given in Fig. 5. In the MATLAB simulation, the all-pass filter (APF) stages were kept ideal and implemented using transfer function, while in the Cadence noise simulation, actual circuit components were used. The noise figure degradation plots highlighted in Fig. 5 were based on the Cadence SpetreRF simulations, assuming a 4-dB baseline RX NF. These simulations were also performed with each tap consuming the same power and contributing the identical amount of noise to the RX signal path.

The tap delay line is modeled as a first-order APF with a transfer function, which is given as [61]

$$H(jw) = \frac{1 - jw\tau}{1 + iw\tau}. (1)$$

Here,  $\tau$  is defined as the time constant. The group delay of the first-order APF can be derived using (1)

$$\tau_g = \frac{2\tau}{1 + (w\tau)^2}.\tag{2}$$

The group delay of the APF is maximized at the frequency of interest when

$$\frac{\partial(\tau_g(\tau))}{\partial \tau} = 0. \tag{3}$$

Fig. 5. Design tradeoff among the number of taps, canceller noise and cancellation BW, and simulations performed in MATLAB Simulink and Cadence SpectreRF.

Solving (3) using (2) reveals that  $\tau_g(jw)$  achieves a maximum when  $\tau = (1/w)$

$$\tau_g(jw)_{\text{max}} = \frac{1}{w} = \frac{1}{2\pi f}.$$

(4)

From (4), the maximum delay for each APF stage is limited by the operating frequency. In this design, the carrier frequency is 2 GHz and the maximum delay for each APF stage is 80 ps. If one applies the sampling theory to analyze the adaptive FIR filter, each tap samples the input signal at a different time and the output of each tap is summed using different gain values. An 80-ps tap-to-tap delay will be equivalent to a sampling frequency of 12.5 GHz, or an oversampling ratio of 3.14. To emulate the TX SI signal, the tap-to-tap delay must be sufficiently small to capture the fastest transient change in the SI signal. In addition, the total APF delay needs to be long enough to cover the SI signal delay spread [62]. The major contributions to SI in the RX are typically the shortest delay paths between the TX and the RX, which include direct coupling and antenna reflection paths [see Fig. 2(c)]. The delay spread between these two paths is approximately 250–350 ps. If the time delay in the RF canceller is designed to suppress the short-latency paths, 4–5 filter taps are sufficient. Additional taps help to suppress the TX leakage paths that arrive at the RX input at a later time, as compared to the two dominant TX-to-RX coupling signal paths. However, more taps will add more active devices and noise to the RX (see Fig. 5). Thus, in this design, it was found that five taps present an optimal based on the desire to achieve a 40-MHz cancellation BW, while minimizing the RX noise figure degradation.

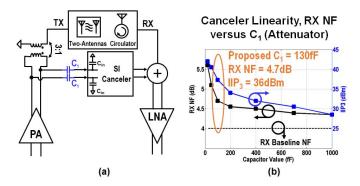

An additional performance challenge associated with the design of both the RF and BB cancellers relates to the need for high linearity. The two feedforward cancellers on this chip take their inputs at the PA output, where the voltage may be large ( $V_{\rm peak} \sim 3$  V). This is in contrast to the canceller output, which is significantly lower in power/voltage amplitude (-15 dBm or 50 mV). Therefore, the linearity bottleneck of this feedforward canceller resides at the interface between the TX output and the canceller input. To accommodate a

Fig. 6. Passive attenuator is introduced at the input of the RF canceller to improve linearity.

Fig. 7. RF canceller linearity versus attenuator capacitor  $C_1$ . (a) Conceptual diagram. (b) Simulation results of the capacitor value versus RX noise figure and canceller IIP<sub>3</sub>.

high-output-power PA, the canceller must be designed to achieve as high a linearity as possible to minimize any intermodulation cross products generated along the feedforward canceller path which are directly injected into the RX, thus degrading the RX sensitivity.

To improve the cancellation paths' linearity performance, a passive attenuator (capacitive divider) was added at the PA—canceller interface (Fig. 6). The attenuator was implemented using a floating capacitor  $C_1$ , which is in series with the input capacitance of the RF canceller  $(C_{in})$  [Fig. 7(a)]. However, any attenuation at the canceller input must be compensated for by providing more active voltage gain in the feedforward canceller, providing sufficient dynamic range at the canceller output, and ensuring gain matching between the TX leakage signal and this feedforward canceller output. As described in [63], additional voltage gain in the canceller signal path will have the effect of introducing/injecting more noise at the LNA/RX input. Thus, while introducing more attenuation in the cancellation path improves its linearity, this also has the effect of degrading the RX noise figure. A simulation illustrating the design tradeoff among the capacitor value, canceller IIP3 and RX noise figure is shown in Fig. 7(b), where one observes that for a lower capacitor value  $C_1$  (which provides a higher attenuation), the linearity improves, while the RX noise figure degrades. For this design, setting  $C_1$

Fig. 8. RF canceller input—output impedance with the impedance seen by the canceller at the input—output. (a) Canceller input swing at 36 dBm IIP<sub>3</sub>. (b) Canceller input—output impedance.

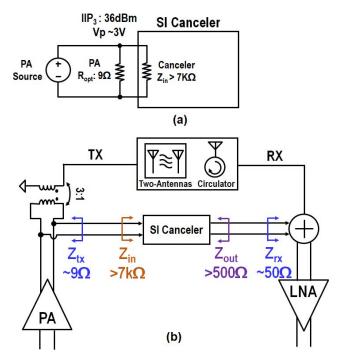

to match  $C_{\rm in}$ , which is 130 fF, provides a good tradeoff among the attenuation (6 dB) at the canceller input, canceller linearity (+36 dBm), and the RX noise figure degradation (0.7 dB). The series capacitor  $C_1$  has the additional benefit of increasing the input impedance looking into the canceller, which minimizes any loading on the PA output stage. For this design, the canceller real part input impedance is larger than 7 k $\Omega$ , which is significantly higher than the  $R_{\rm opt}$  of the PA (see Fig. 8).

To further improve the linearity, the inputs of both cancellers are connected to the primary side of the PA output transformer that has a significantly lower impedance ( $R_{\rm opt} \sim 9~\Omega$ ) as compared to the secondary side of the transformer that is connected to the 50- $\Omega$  antenna impedance. As such, the peak voltage on the primary side of the transformer (canceller input) is significantly lower ( $V_{\rm peak} \sim 3~V$ ), thus helping to further improve the canceller input-referred linearity. However, similar to the case of adding an attenuator (capacitor) at the canceller input to improve the linearity, tapping off the lowest impedance node at the PA output will reduce the effective canceller power gain, as described as

Canceller power gain =

$$10 \cdot \log_{10} \left( A_v^2 \cdot \frac{Z_{tx}}{Z_{rx}} \right)$$

. (5)

Here,  $A_v$  is the canceller voltage gain, and  $Z_{tx}$  and  $Z_{rx}$  are the impedance from the perspective of the canceller input and output looking back into the TX and the RX, respectively. As an example, if  $Z_{tx}$  is 9  $\Omega$  and  $Z_{rx}$  is 50  $\Omega$ , this gives a 7.4-dB power attenuation due to the impedance transformation. To compensate for this power loss, the canceller signal path must provide an additional 7.4 dB of active voltage gain, which for this design was done with minimal impact on the RX NF.

Fig. 9. Block-level diagram of the baseband cancellation path.

Fig. 10. Baseband canceller for attenuation of a TX carrier signal.

A high canceller output impedance is achieved using nonminimum length devices (L=65 nm). The  $R_o$  looking into the canceller output is greater than 500  $\Omega$ , which is significantly higher than the LNA input impedance, thus having minimal impact on the LNA input matching network and  $S_{11}$ .

# B. Second Baseband Canceller Signal Path

The design methodology for the BB canceller is similar to that of the RF canceller with a few significant differences that include: 1) using a larger time delay between the filter coefficients and 2) exploiting the use of highly correlated local oscillators to reduce the effects of reciprocal mixing of the TX leakage signal. The second BB cancellation path uses a downconversion mixer to translate the carrier frequency to BB. The BB feedforward canceller benefits from the cancellation signal being injected into the RX backend (analog BB). As such, there is significant RX gain prior to injection of the cancellation signal, thus relaxing the required noise performance of the BB canceller.

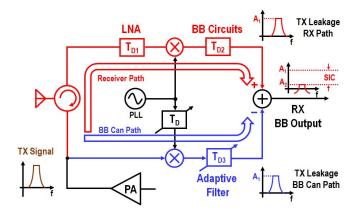

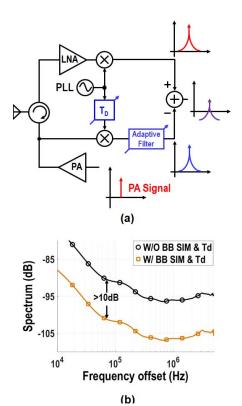

The BB cancellation path contains a 14-tap complex analog adaptive FIR filter with a downconversion quadrature mixer (Fig. 9). The BB canceller serves two functions: 1) it attenuates the TX SI carrier signal as well as the noise and non-linearities generated by the PA and TX and 2) it cancels the TX SI reciprocal mixing with the LO phase noise in the RX signal path. These concepts are described in the following.

The TX SI carrier signal travels in two paths. In one path, the TX SI signal passes through the circulator and down the RX chain, while in the other path, it travels through the BB canceller (see Fig. 10). Cancellation of the SI reciprocal

Fig. 11. Baseband canceller used to attenuate the TX leakage signal reciprocal mixing with LO phase noise in RX signal path.

mixing in the RX and BB cancellation path mixers is achieved, if these two paths are matched in time. This design implements a combination of variable time delay blocks that includes  $T_D$  and  $T_{D3}$  to match the delay in the RX and the BB canceller signal paths (see Fig. 10).

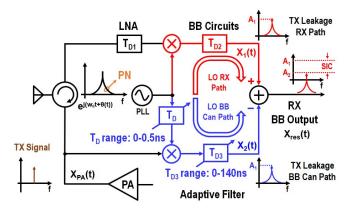

The BB cancellation path attenuates the effects of reciprocal mixing between the TX SI signal and the LO phase noise in the RX signal path. This is shown conceptually, and for simplicity, as a single-tone continuous wave (CW) tone at the TX output (Fig. 11). Since the LO that supplies both the RX and BB cancellation path is derived from the same synthesizer, the phase noise of the LOs associated with the RX and BB canceller paths is highly correlated. Thus, if the time delays in the RX and BB cancellation paths are matched, the phase noise associated with the TX SI signal can be cancelled. A more mathematical analysis for this approach to cancel the TX SI reciprocal mixing products is given in the Appendix.

Intuitively, the adaptive FIR filter in the signal path of the BB canceller ( $T_{D3}$  in Fig. 11) matches any delay introduced by the BB circuitry in the RX signal path ( $T_{D2}$ ). The additional delay in the LO path ( $T_D$ ) is tunable to match the delay introduced from the circulator and front-end LNA ( $T_{D1}$ ).

The above-mentioned analysis assumes a single short-delay leakage path. In the more realistic case with multiple leakage paths, including environmental reflections arriving with longer delays, this approach will be challenged to completely cancel the product of TX SI reciprocal mixing with the LO phase noise in the RX path. However, interference due to reflections with longer delays is received at a significantly lower power as compared to leakage paths with a short delay (e.g., direct coupling through the circulator). SI with lower power levels at the RX input results in reciprocal mixing products that are closer to the RX noise floor, having less impact on the carrier-to-interference ratio at the RX output. Thus, for this transceiver, a single delay unit  $(T_D)$  is designed to provide a compromise among the cancellation performance, power consumption, and silicon area.

Although the phase noise at both mixer ports due to the synthesizer and VCO is highly correlated, any phase noise introduced by the interconnect and circuitry (e.g., LO buffers and variable delay cell) along the two independent paths between the VCO and the mixers has no correlation. However,

Fig. 12. System block diagram of components on the 40-nm CMOS FD system.

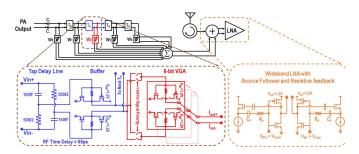

Fig. 13. Transistor-level implementation of the five-tap FIR-based RF canceller and the low-noise amplifier.

the phase noise associated with a VCO and synthesizer often dominates any phase noise contributed by open-loop buffers and interconnect, particularly close to the carrier. This relates to the fact that noise inside a synthesizer is correlated, integrating from one period to the next, while broadband thermal noise introduced by buffers, interconnect, or delay cells outside the synthesizer loop lack an integrative process. In this design, the measured phase noise floor of the synthesizer is  $-155~\mathrm{dBc/Hz}$ ; however, the simulated noise produced by the variable delay cell is  $-167~\mathrm{dBc/Hz}$ , resulting in minimal impact on the RX NF. Post-cancellation, a potential major source of phase noise and reciprocal mixing, could come from the noise generated by the delay cells and buffers, in the two independent LO paths.

#### IV. CIRCUIT IMPLEMENTATION

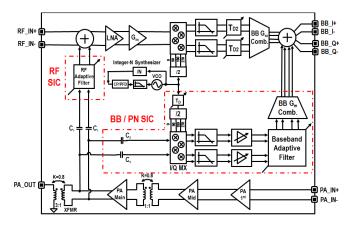

A block diagram of the dual injection-path FD front-end transceiver is shown in Fig. 12, which illustrates all the components integrated on the chip. This chip includes an RX chain from the LNA input to an analog BB output, an integer-*N* PLL, a noise cancelling PA, and two integrated feedforward cancellers. All the signal paths are designed differentially to minimize the TX-to-RX isolation, while improving the even-order distortion performance.

#### A. RF Canceller and RX LNA

The RF canceller is made up of a five-tap analog FIR filter (Fig. 13). Each of the tap delay lines is implemented using a

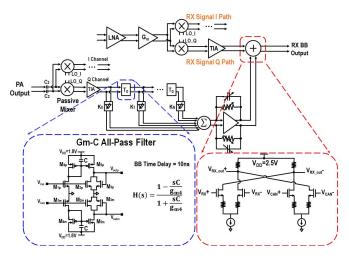

Fig. 14. Transistor-level implementation of the 14-tap FIR-based BB canceller with the output summing stage.

passive RC-CR first-order APF. This APF functions as a truetime delay cell with a nominal delay of 65 ps. The variable gain amplifier (VGA) was implemented as a 6-bit inverterbased amplifier with one additional bit that determines the signal polarity. An additional bit in the VGA will provide 6 dB more dynamic range and better cancellation; however, this also has the effect of reducing the output impedance of the canceller by half, loading the impedance at the LNA input, which increases the RX input insertion loss. The RF canceller was designed with a gain range from -60 to -25 dB to emulate the magnitude response of the leakage channel. The maximum gain of the RF canceller is set to 5 dB higher than the expected magnitude of the maximum leakage signal to provide some design margin. A unity-gain buffer stage was added between each tap delay to buffer each of the APFs. The output of each filter/gain stage is summed in the current domain, with the ac signal coming from the RX input (antenna) (Fig. 13). The RX LNA uses resistive feedback to achieve a broadband 50- $\Omega$  match (Fig. 13) [64], [65]. A CMOS implementation of the LNA increases the effective  $G_m$  by nearly a factor of 2, which aids in reducing the LNA noise figure. A source follower is added to avoid the direct feedforward path from the LNA input to the output, which effectively increases the LNA output impedance, gain, and improves the NF [66].

#### B. Baseband Canceller

The BB cancellation path is implemented with two 14-tap analog FIR filters and a passive downconversion mixer (see Fig. 14). Each of the tap-delay elements have a desired delay significantly higher (10 ns) than the RF analog FIR. If the same RC–CR circuit was used to realize the delays as was done at RF, the on-chip implementation would be prohibitively large (at least  $10\times$  as compared to the RF equivalent. Thus, the BB FIR tap-delay elements were implemented using a compact  $G_m$ -C-based APF described in [67]–[69]. The output of each tap is summed in the current domain, then translated to the voltage domain using a transimpedance amplifier. The BB

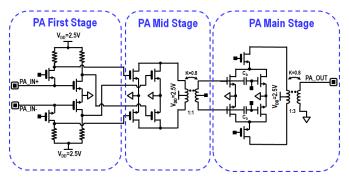

Fig. 15. Transistor-level implementation of the three-stage class AB power amplifier.

canceller signal is combined with the desired RX signal using a resistor-degenerated common-source amplifier (Fig. 14). The BB canceller simulated flicker noise corner is 500 kHz, which minimizes the impact on the RX NF.

#### C. Power Amplifier

This FD radio integrates a three-stage class-AB PA (Fig. 15), with the input coming from an off-chip signal generator. A common-source, common-gate noise-cancelling topology, which is similar to what has been often used in low-noise amplifier designs, is implemented as the first stage of the PA, to reduce the PA thermal noise floor [70], [71]. It is worth noting that the PA noise cancelling topology is only beneficial when the rest of TX is off chip, and the PA demands  $50\Omega$  input impedance; a fully integrated TX would likely not benefit from this topology. To improve the linearity of the PA, a  $G_m$ -linearization technique was realized similar to [72] and [73]. The input devices of the PA output stage are divided into two separate devices. The larger device is biased closer to the class-A region, while the auxiliary device is biased closer to the class-B region to linearize the effective  $G_m$  over a wide range of the input voltages. The PA operates off a 2.5 V supply.

#### D. Remaining Integrated Transceiver Components

The RX chain contains a low-noise amplifier,  $G_m$  stage, and passive mixers, followed by a transimpedance amplifier. The mixer is driven by a four-phase 25% duty cycle LO, which was generated from a divide-by-two circuit [74]. The tunable time delay cell in the LO path, used for the BB canceller (see Fig. 10), implements a current starving topology, which is similar to [60] and [75] and has a simulated resolution (LSB) of 0.5 ps with a tuning range of more than one period of the carrier. This is equivalent to a  $0.36^{\circ}$  resolution with a 0.5-ns tuning range at 2 GHz. To improve the phase noise performance of the integer-N synthesizer, an impulse sensitivity function (ISF) manipulation technique similar to [76] is used to lower the phase noise performance of the voltage-controlled oscillator.

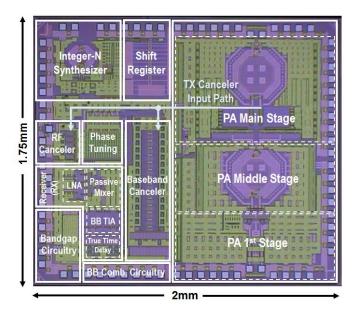

The chip was fabricated in a 40-nm six-metal-layer Taiwan semiconductor manufacturing company (TSMC) CMOS process and occupies an area of  $1.75 \text{ mm} \times 2 \text{ mm}$  that includes the bond pads (Fig. 16). The chip was wire bonded directly to the test-board using chip-on-board packaging.

Fig. 16. FD die photograph. Device implemented in a six-metal-layer TSMC 40 nm.

Fig. 17. Measurement setup for the FD chip.

#### V. MEASUREMENT RESULTS

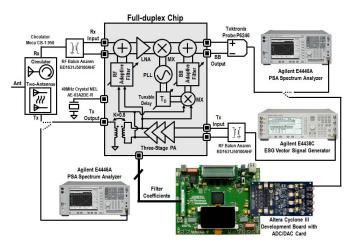

To test the functionality of the proposed FD chip, the standard RF measurements were performed to characterize the gain, noise, linearity, and depth/BW of SI cancellation with the cancellers enabled and disabled; the measurement setup is shown in Fig. 17. During testing, there was an option of using two configurations for the RF front-end interface, mainly either two antennas or a discrete circulator (MECA Electronics: CS-1.950), both of which could provide an isolation as high as 30 dB. An air interface that is realized with two antennas typically has a group delay larger than 2 ns, and thus, there will be a non-negligible time delay mismatch between the RF canceller (range 250-350ps) and the leakage channel (>2 ns), which will lead to less cancellation in the RF domain. The cable routing from the chip TX output to the circulator, to the RX input, were kept as short as possible, to minimize the delay mismatch between the leakage and the cancellation paths. Two surface-mount singled-ended-todifferential baluns (Anaren: BD1631J50100AHF) were used to present a balanced input to both the RX and the TX input. The RX BB quadrature output signals were connected to two low-noise high-input-impedance (>200 k $\Omega$ , <1 pF) active differential probes (Tektronix: P6246), to buffer the chip BB outputs, while providing 50- $\Omega$  matching to the next stage, which could be either a spectrum analyzer (Agilent E4440A) or a discrete 14-bit 140-MSPS analog-to-digital converter (Analog Devices: AD9254). The reference clock of the integer-N synthesizer uses a low-noise crystal oscillator (NEL Frequency Controls: AE-03A2DE-R/40.000 MHz). Section V begins with the circulator serving as the leakage channel, where the antenna port is connected to a 50- $\Omega$  termination. Another set of measurements using two antennas is provided with a discussion, at the end of this section.

While performing closed-loop TX SI cancellation testing, a CW or modulated signal was applied to the PA input from a vector signal generator (Agilent E4438C). The analog-todigital converter (ADC) sampled the RX BB output signal, which was a downconverted version of the TX SI signal, averaged the RX BB signal over ten cycles, and then sent it back to an field programmable gate array (FPGA) board (Altera Cyclone III EP3C120 Development Board) for postprocessing. The FPGA board emulates what would otherwise be a digital BB to implement a closed-loop calibration for the analog FIR filters in both the feedforward cancellation paths and the tunable delay element used to suppress the reciprocal mixing of the TX SI. A blind source adaptation algorithm was used to adapt the coefficients of all the filter taps, where the algorithm begins the adaption process on the five-tap RF canceller first. After the RF canceller filter taps converge, the adaptation algorithm then calibrates the BB complex IQ cancellation filters.

All measurements were taken using five different test boards and chips.

#### A. Standard RF Measurements

The RX operates from 1.7 to 2.2 GHz with a measured maximum gain of 36 dB, 3-dB BW of 12 MHz, and a 4-dB in-band noise figure. The measured in-band IIP<sub>3</sub> and  $P_{-1\,dB}$  of the RX is -5 and -15 dBm, respectively. The entire RX consumes 22 mW from a 1.2-/2.5-V power supply.

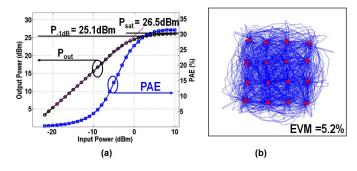

The PA has a measured output  $P_{-1\,dB}/P_{sat}$  of 25.1/26.5 dBm and a maximum PAE of 32% [see Fig. 18(a)]. The PA error vector magnitude (EVM) was measured to be 5.1% EVM when a 40 Mb/s 16QAM signal with +20-dBm output power was used [see Fig. 18(b)].

The integer-N synthesizer has a measured locking range from 3.4 to 4.4 GHz, while consuming 10.4 mW from a 1.2-V supply with a phase noise of -116 dBc/Hz @ 1 MHz offset at a center frequency of 4 GHz. The reference spur of the synthesizer is -55 dBc.

The RF/BB canceller is supplied by 1.2/1.8 V and has a measured  $P_{-1\,dB}$  and IIP<sub>3</sub> of 27/26.5 and 36/34.5 dBm, respectively. These linearity numbers were reported using a two-tone test by enabling only the last taps of RF/BB canceller with a maximum gain, while disabling the remaining taps. The

Fig. 18. Measured PA performance. (a) PA output power and efficiency with a single tone input at 1.96 GHz. (b) PA EVM testing with an input of 40 Mbp/s 16-QAM signal and an average PA output power of 20 dBm at a center frequency of 1.96 GHz.

two-tone signals were injected at the output of TX (canceller input), and the intermodulation products were measured at the RX input. During the measurement, the PA was turned on to provide a low impedance ( $R_{\rm opt} \sim 9~\Omega$ ) at the canceller input. The transformer insertion loss was de-embedded from the measurement based on the simulation results (IL  $\sim 1.5~{\rm dB}$ ). The purpose of this measurement was to characterize the worst case linearity of the canceller, since the last taps see the most gain and are the dominant contributor of non-linearities in the active canceller chain, thus leading to a worst case linearity performance. When the same measurements were repeated using only the first tap of the RF canceller, the results of  $P_{-1~{\rm dB}}$  and IIP3 are to be improved to 32 and 42.5 dBm, respectively.

### B. SI Cancellation Measurements With Circulator

To characterize the functionality of the feedforward cancellers, both CW and modulated signals were applied to the TX input, while both the cancellation depth and the BW were measured by observing the residual TX SI at the RX BB output. The RX 3-dB BW is 12 MHz, which is insufficiently high to allow a flat response in the BB. This was a design oversight on the chip, as the BB I/Q BW should be higher than 20 MHz for a 40-MHz signal. However, the measurement was taken with the canceller both on and off using the narrower BW (12 MHz). Thus, the reported cancellation number is independent of the RX BB band edge.

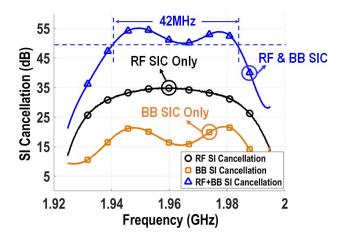

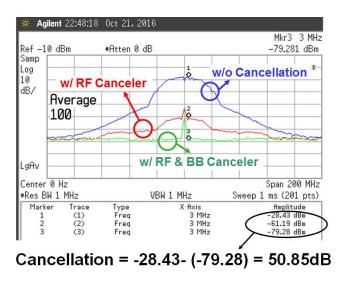

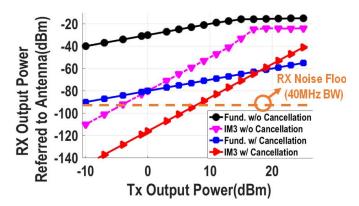

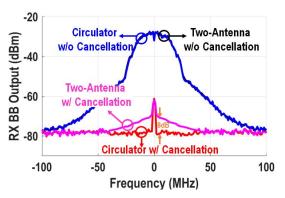

Applying a CW signal to the PA input, the cancellation BW was measured in two steps. First, the cancellation was maximized at a center frequency by adapting the coefficients of both cancelling filters. Then, while holding the feedforward FIR filter settings, a series of CW signals with different frequencies were swept across the band. This measurement reveals that a minimum 50-dB cancellation was achieved within the 42-MHz cancellation BW (see Fig. 19). The TX SI cancellation measurement was then repeated using a modulated signal. A 40 MHz 16QAM signal with an average output power of 15 dBm was applied to the TX input, while the RX output spectrum was measured with both the cancellation network enabled and disabled. From these measurements, more than 50 dB of SI cancellation was achieved, which is consistent with the test results when using a CW input (see Fig. 20).

Fig. 19. Measurement results of TX SI suppression versus bandwidth.

Fig. 20. Measured TX suppression using a modulated 40 Mb/s 16QAM signal. RX baseband output spectrum with cancellers enabled and disabled.

A two-tone test was performed to characterize the canceller linearity performance. This measurement was taken by applying two in-band tones with equal amplitude to the canceller input while the RX BB output was measured, in the case of the cancellers enabled and disabled (see Fig. 21). When the cancellers are enabled, the amplitude of third-order intermodulation products generated by the cancellers is equivalent to the fundamental tone at a 17-dBm PA output power. If the PA is operated above 17 dBm, the residual SI signal after cancellation will be limited by the canceller third-order non-linearity. The canceller linearity could be further improved by adding more attenuation at the canceller input, which will be traded off with the RX noise figure (see Fig. 7). The canceller effective IIP<sub>3</sub> with respect to RX/antenna input, while testing the SI cancellation testing is +17 dBm.

The required IM3 in the link budget depends on the modulation scheme. In a multi-carrier system, if the PA operates at 10 dBm or higher, the absolute IM3 generated by the canceller is still above the RX noise floor. Thus, in order to operate this PA with full power (25 dBm) in the FD mode, the canceller

Fig. 21. Two-tone linearity testing for the cancellers, measured with two tones and IM3 components of the TX SI signal all referred to the antenna with the cancellers enabled and disabled.

Fig. 22. Measured RX noise figure with +15-dBm blocker with the canceller enabled and disabled relative to the baseband frequency.

IIP<sub>3</sub> needs to be as high as 50 dBm to guarantee that the canceller-generated IM3 is lower than the RX noise floor. In contrast, the IIP<sub>3</sub> required of the canceller would be relaxed if the radio was operating with a modulated signal using a single-carrier.

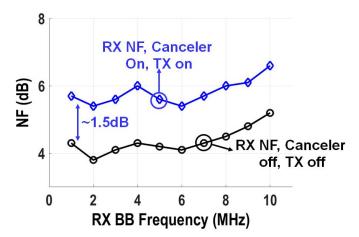

The RX NF degradation due to the introduction of the feedforward cancellers is another key performance metric to adequately characterize the FD transceiver. The RX NF measurements in FD mode were performed using a desired single-tone RX signal, which were set 100 kHz away from the TX carrier signal, while monitoring the carrier-to-interference (C/I) ratio at the RX BB output; the results are shown in Fig. 22. The black curve is the measured RX baseline NF with the TX turned off and the canceller disabled. Next, the TX is enabled with the PA output set to 15 dBm. After enabling both cancelling filters, the RX NF degradation was determined to be 1.55 dB.

To characterize the cancellation of TX SI signal reciprocal mixing with the LO phase noise in the RX signal path, a CW signal is applied to the PA input while the RX BB output spectrum is measured, with the BB canceller and the additional time delay block  $T_D$ , enabled and disabled [see Fig. 23(a)]. The measurement result shows a 10-dB suppression [see Fig. 23(b)].

Fig. 23. Measured suppression of the TX SI signal reciprocal mixing with RX LO phase noise in the RX signal path. (a) Measurement setup. (b) Measurement results at the RX baseband output with cancellation enabled and disabled.

Fig. 24. Measured TX suppression using a modulated 40 Mb/s 16QAM signal with a circulator and two-antenna as leakage channel. RX baseband output spectrum with cancellers enabled and disabled.

## C. SI Cancellation Measurements With Two-Antennas

The SI cancellation measurement was repeated using two antennas to serve as the air interface. The leakage channel from two antennas can produce a group delay up to ~2 ns. The SI cancellation results using a modulated signal (40 Mb/s 16-QAM) are shown in Fig. 24. The larger group delay introduced from the two antennas creates a nonnegligible time delay mismatch between the leakage path and the RF canceller. This degrades the cancellation by 8 dB (worst case) as compared to using an air interface that includes a circulator and a single antenna.

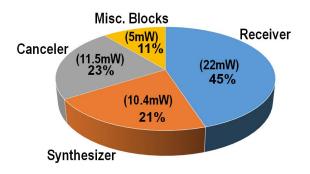

The total chip power consumption is 49 mW, excluding the PA (see Fig. 25). A comparison and performance summary is shown in Table I.

TABLE I Comparison and Performance Summary

|                                                    |                   | J. Zhou<br>ISSCC' 2015           | DJ van den Broek<br>ISSCC' 2015 | D. Yang<br>JSSC' 2015         | J. Zhou<br>ISSCC' 2016           | This Work                                           |

|----------------------------------------------------|-------------------|----------------------------------|---------------------------------|-------------------------------|----------------------------------|-----------------------------------------------------|

| Architecture                                       |                   | Frequency Domain<br>Equalization | Mixer-First RX+<br>VM-downmixer | Mixer First+<br>Duplexing LNA | Integrated Circulator+ BB<br>SIC | Adaptive Filter + NC PA+<br>LO Sideband Suppression |

| Technology/VDD                                     |                   | 65nm /?                          | 65nm/1.2V                       | 65nm/1.2V, 2.5V               | 65nm/1.3V, 2.2V                  | 40nm /1.2, 1.8V, 2.5V                               |

| RX Frequency (GHz)                                 |                   | 0.8-1.4                          | 0.15-3.5                        | 0.1-1.5                       | 0.6-0.8                          | 1.7-2.2                                             |

| TX-to-RX Interface Isolation (dB)                  |                   | 30-50                            | N/A                             | N/A                           | N/A                              | 30-35                                               |

| Integrated Power Amplifier                         |                   | No                               | Yes                             | Yes                           | No                               | Yes                                                 |

| Integrated PLL                                     |                   | No                               | No                              | No                            | No                               | Yes                                                 |

| TX Maximum Suppression (dB)                        |                   | N/A                              | 27                              | 33                            | N/A                              | 55                                                  |

| Cancellation<br>BW                                 | Cancellation (dB) | 20                               | 27                              | 33                            | 42*                              | 50                                                  |

|                                                    | BW (MHz)          | 15 / 25°                         | 16.25°                          | 0.3                           | 12'                              | 42                                                  |

| RX NF degradation due to leakage cancellation (dB) |                   | 0.9-1.2/1.1-1.5                  | 4-6                             | N/A*                          | 5.99                             | 1.05 (RF)+0.5(BB)                                   |

| Canceler Power Consumption (mW)                    |                   | 44-91 <sup>b</sup>               | N/A                             | N/A                           | 30                               | 3.5 (RF) +8 (BB)                                    |

| RX IB IIPa (dBm)                                   |                   | -20 @ 27dB gain                  | +9/19 at 24dB gain              | -38.7 @ 53dB gain             | -33 at 42dB gain                 | -5 at 30dB gain                                     |

| RX In-Band SC-FD P-tes with Cancellation (dBm)     |                   | >-8                              | >1.5                            | -17.3                         | N/A                              | +3                                                  |

| Effective IIPs with respect to RX/ANT Input (dBm)  |                   | +2 at 27dB gain                  | 21.5 at 24dB gain               | N/A                           | +1 at 42dB gain                  | +17 at 30dB gain                                    |

| RF Canceler Area (µm²)                             |                   | N/A                              | N/A                             | N/A                           | N/A                              | 203 × 124                                           |

| Canceler IIP₃ (dBm)                                |                   | N/A                              | N/A                             | N/A                           | N/A                              | 36 (RF) / 34.5 (BB)                                 |

| Canceler P-1dB (dBm)                               |                   | N/A                              | N/A                             | N/A                           | N/A                              | 27 (RF) / 26.5 (BB)                                 |

| RX LO Sideband Suppression (dB)                    |                   | N/A                              | N/A                             | N/A                           | N/A                              | 10                                                  |

| RX Gain                                            |                   | 27-42                            | 24                              | 33-53                         | 42                               | 20-36                                               |

| RX Power Consumption (mW)                          |                   | 63-69                            | 23-56°                          | 43-56                         | 70°                              | 22                                                  |

| Maximum TX Output Power (dBm)                      |                   | N/A                              | >10                             | N/A                           | N/A                              | 25                                                  |

| TX PAE (%) @Maximum Power                          |                   | N/A                              | N/A                             | N/A                           | N/A                              | 32                                                  |

| TX EVM (%)                                         |                   | N/A                              | N/A                             | N/A                           | N/A                              | 5.1                                                 |

| PLL Phase Noise @1MHz (dBc/Hz)                     |                   | N/A                              | N/A                             | N/A                           | N/A                              | -116                                                |

| Active Area (mm²)                                  |                   | 4.8                              | 2                               | 1.5                           | 1.4                              | 3.5                                                 |

<sup>\*</sup> Measurement with an antenna pair. 15MHz BW, 0.9-1.2dB NF deg. is with one filter. 25MHz, 1.1-1.5dB NF deg. is with two filters. b Power including 0.47mW Gm cells and 44mW LO for one filter.

The measured maximum 55dB cancellation and 50dB cancellation over 40MHz BW doesn't include the 30-35 dB isolation from the discrete circulator or two-antennas.

Fig. 25. FD transceiver power breakdown. This excludes the PA that dissipates up to 1 W.

#### VI. CONCLUSION

This paper demonstrates a dual-injection path FD wireless transceiver system that achieves a combination of the broadest cancellation BW (>42 MHz) with the highest SI cancellation (>50 dB), compared to the state of the art. The proposed front end includes two feedforward cancellers, which are both implemented as analog FIR filters to provide an inverse response of the leakage channel. The first coarse canceller is attached at the RX input to relax the linearity requirements of LNA and the subsequent RX blocks, while the second finer canceller injects its output into the RX BB.

Future wireless applications could potentially have both the FD and FDD modes. When network traffic is low, FDD would likely be more optimal from a power consumption perspective. With more wireless traffic and a demand for higher data rates, the device would have the option of moving to a FD mode of communication.

#### APPENDIX

$X_{\rm PA}(t)$  is the PA output signal, and  $X_1(t)$  and  $X_2(t)$  are the leakage and canceller signal before the summing stage

<sup>°</sup>Half-duplex/Full-duplex mode show NF of 6.3/10.3-12.3dB. Power including LO tree. \*RX DSB NF is 5-8dB in Full-Duplex mode.

<sup>&</sup>lt;sup>†</sup>42dB cancellation 12MHz BW measured including integrated circulator, not including 43dB digital cancellation from Matlab.

The TDD RX NF is 5dB, NF increases to 8.4dB including the circulator and goes to 10.9dB including the baseband canceller. Power Including 60mW signal path and 10mW LO path at 0.7GHz.

(Fig. 11). The LO signal with phase noise is modeled with  $e^{j(w_0t+\theta(t))}$ . In this analysis, we assume that there is no amplitude mismatch between the leakage and the canceller signal. From Fig. 11,  $X_1(t)$  and  $X_2(t)$  could be derived as

$$X_1(t) = X_{PA}(t - T_{D1} - T_{D2}) \times e^{j(w_0(t - T_{D2}) + \theta(t - T_{D2}))}$$

(6)

$$X_2(t) = X_{PA}(t - T_{D3}) \times e^{j(w_0(t - T_D - T_{D3}) + \theta(t - T_D - T_{D3}))}.$$

(7)

In order to achieve TX SI cancellation,  $X_1(t)$  and  $X_2(t)$ have to be equal, therefore combining (6) and (7) gives

$$T_{D3} = T_{D1} + T_{D2} (8)$$

$$T_D = -T_{D1}. (9)$$

In this design,  $T_D$  is implemented with a digital variable time delay block that has a tuning range of one carrier cycle; therefore,  $T_D$  could also be modeled as a 360° phase rotator. Moreover, the negative sign in (9) could be realized with a simple 180° phase shift.

#### ACKNOWLEDGMENT

The authors would like to thank L. Lin, D. Yee, D. J. Allstot, S. Roy, and V. Sathe for assisting this paper.

#### REFERENCES

- [1] F. Khan, "Multi-comm-core architecture for terabit-per-second wireless," IEEE Commun. Mag., vol. 54, no. 4, pp. 124-129, Apr. 2016.

- [2] T. X. Tran, A. Hajisami, P. Pandey, and D. Pompili, "Collaborative mobile edge computing in 5G networks: New paradigms, scenarios, and challenges," IEEE Commun. Mag., vol. 55, no. 4, pp. 54-61, Apr. 2017.

- M. Lauridsen, L. C. Gimenez, I. Rodriguez, T. B. Sorensen, and P. Mogensen, "From LTE to 5G for connected mobility," IEEE Commun. Mag., vol. 55, no. 3, pp. 156-162, Mar. 2017.

- [4] M. Ayyash et al., "Coexistence of WiFi and LiFi toward 5G: Concepts, opportunities, and challenges," IEEE Commun. Mag., vol. 54, no. 2,

- [5] D. Bharadia, E. McMilin, and S. Katti, "Full duplex radios," in Proc. ACM SIGCOMM Conf. SIGCOMM, New York, NY, USA, 2013, pp. 375-386.

- [6] J. I. Choi, M. Jain, K. Srinivasan, P. Levis, and S. Katti, "Achieving single channel, full duplex wireless communication," in Proc. ACM MobiCom, New York, NY, USA, 2010, pp. 1-12.

- [7] M. Jain et al., "Practical, real-time, full duplex wireless," in Proc. ACM

- MobiCom, New York, NY, USA, 2011, pp. 301–312.

A. Yadav, O. A. Dobre, and N. Ansari, "Energy and traffic aware full-duplex communications for 5G systems," IEEE Access, vol. 5, pp. 11278-11290, 2017.

- S. H. Chae and K. Lee, "Degrees of freedom of full-duplex cellular networks: Effect of self-interference," IEEE Trans. Commun., vol. 65, no. 10, pp. 4507-4518, Oct. 2017.

- [10] D. Liu, Y. Shen, S. Shao, Y. Tang, and Y. Gong, "On the analog selfinterference cancellation for full-duplex communications with imperfect channel state information," IEEE Access, vol. 5, pp. 9277-9290, 2017.

- [11] R. K. Mungara, I. Thibault, and A. Lozano, "Full-duplex MIMO in cellular networks: System-level performance," *IEEE Trans. Wireless* Commun., vol. 16, no. 5, pp. 3124-3137, May 2017.

- [12] K. E. Kolodziej, B. T. Perry, and J. G. McMichael, "Multitap RF canceller for in-band full-duplex wireless communications," IEEE Trans. Wireless Commun., vol. 15, no. 6, pp. 4321-4334, Jun. 2016.

- [13] G. Prasad, L. Lampe, and S. Shekhar, "In-band full duplex broadband power line communications," IEEE Trans. Commun., vol. 64, no. 9, pp. 3915-3931, Sep. 2016.

- [14] D. Korpi, M. Heino, C. Icheln, K. Haneda, and M. Valkama, "Compact inband full-duplex relays with beyond 100 dB self-interference suppression: Enabling techniques and field measurements," IEEE Trans. Antennas Propag., vol. 65, no. 2, pp. 960-965, Feb. 2017.

- [15] D. Korpi et al., "Full-duplex mobile device: Pushing the limits," IEEE Commun. Mag., vol. 54, no. 9, pp. 80-87, Sep. 2016.

- [16] V. Syrjala, M. Valkama, M. Allen, and K. Yamamoto, "Simultaneous transmission and spectrum sensing in OFDM systems using full-duplex radios," in Proc. IEEE 82nd Veh. Technol. Conf. (VTC-Fall), Sep. 2015, pp. 1–6.

- [17] D. Korpi, T. Riihonen, V. Syrjälä, L. Anttila, M. Valkama, and R. Wichman, "Full-duplex transceiver system calculations: Analysis of ADC and linearity challenges," IEEE Trans. Wireless Commun., vol. 13, no. 7, pp. 3821-3836, Jul. 2014.

- D. Korpi, L. Anttila, V. Syrjälä, and M. Valkama, "Widely linear digital self-interference cancellation in direct-conversion fullduplex transceiver," IEEE J. Sel. Areas Commun., vol. 32, no. 9, pp. 1674-1687, Sep. 2014.

- [19] K.-D. Chu, M. Katanbaf, C. Su, T. Zhang, and J. C. Rudell, "Integrated CMOS transceivers design towards flexible full duplex (FD) and frequency division duplex (FDD) systems," in Proc. IEEE Custom Integr. Circuits Conf. (CICC), Apr. 2018.

- [20] T. Zhang, A. Najafi, C. Su, and J. C. Rudell, "A 1.7-to-2.2 GHz full-duplex transceiver system with >50 dB self-interference cancellation over 42 MHz bandwidth," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2017, pp. 314-315.

- [21] J. Zhou, T. H. Chuang, T. Dinc, and H. Krishnaswamy, "Receiver with > 20 MHz bandwidth self-interference cancellation suitable for FDD, coexistence and full-duplex applications," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2015, pp. 1-3.

- [22] J. Zhou, N. Reiskarimian, and H. Krishnaswamy, "Receiver with integrated magnetic-free N-path-filter-based non-reciprocal circulator and baseband self-interference cancellation for full-duplex wireless," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Jan. 2016, pp. 178-180.

- N. Reiskarimian, M. B. Dastjerdi, J. Zhou, and H. Krishnaswamy, "Highly-linear integrated magnetic-free circulator-receiver for fullduplex wireless," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2017, pp. 316-317.

- [24] D. Yang, H. Yüksel, and A. Molnar, "A wideband highly integrated and widely tunable transceiver for in-band full-duplex communication," IEEE J. Solid-State Circuits, vol. 50, no. 5, pp. 1189-1202, May 2015.

- T. Zhang, "Integrated wideband self-interference cancellation techniques for FDD and full-duplex wireless communication," Ph.D. dissertation, Dept. Elect. Eng., Univ. Washington, Seattle, WA, USA,

- [26] T. Dinc and H. Krishnaswamy, "A T/R antenna pair with polarizationbased reconfigurable wideband self-interference cancellation for simultaneous transmit and receive," in IEEE MTT-S Int. Microw. Symp. Dig., May 2015, pp. 1-4.

- T. Dinc and H. Krishnaswamy, "Millimeter-wave full-duplex wireless: Applications, antenna interfaces and systems," in Proc. IEEE Custom Integr. Circuits Conf. (CICC), Apr. 2017, pp. 1-8.

- [28] T. Dinc, A. Chakrabarti, and H. Krishnaswamy, "A 60 GHz CMOS full-duplex transceiver and link with polarization-based antenna and RF cancellation," IEEE J. Solid-State Circuits, vol. 51, no. 5, pp. 1125-1140, May 2016.

- [29] J. Zhou et al., "Integrated full duplex radios," IEEE Commun. Mag., vol. 55, no. 4, pp. 142-151, Apr. 2017.

- [30] Y.-H. Kao, H.-C. Chou, C.-C. Peng, Y.-J. Wang, B. Su, and T.-S. Chu, "A single-port duplex RF front-end for X-band single-antenna FMCW radar in 65 nm CMOS," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2017, pp. 318-319.

- [31] S. Ramakrishnan, L. Calderin, A. Niknejad, and B. Nikolić, "An FD/FDD transceiver with RX band thermal, quantization, and phase noise rejection and >64 dB TX signal cancellation," in Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC), Jun. 2017, pp. 352-355.

- [32] B. Debaillie et al., "Analog/RF solutions enabling compact full-duplex radios," IEEE J. Sel. Areas Commun., vol. 32, no. 9, pp. 1662-1673, Sep. 2014.

- [33] B. Debaillie et al., "RF self-interference reduction techniques for compact full duplex radios," in Proc. IEEE 81st Veh. Technol. Conf. (VTC Spring), May 2015, pp. 1-6.

- [34] K.-D. Chu, M. Katanbaf, T. Zhang, C. Su, and J. C. Rudell, "A broadband and deep-TX self-interference cancellation technique for fullduplex and frequency-domain-duplex transceiver applications," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2018, pp. 170–171.

- T. Zhang, A. R. Suvarna, V. Bhagavatula, and J. C. Rudell, "An integrated CMOS passive self-interference mitigation technique for FDD radios," IEEE J. Solid-State Circuits, vol. 50, no. 5, pp. 1176-1188, May 2015.

- [36] T. Zhang, A. R. Suvarna, V. Bhagavatula, and J. C. Rudell, "An integrated CMOS passive transmitter leakage suppression technique for FDD Radios," in *Proc. IEEE Radio Freq. Integr. Circuits (RFIC) Symp.*, Jun. 2014, pp. 43–46.

- [37] J. C. Rudell, T. Zhang, and A. R. Suvarna, "Systems, transceivers, receivers, and methods including cancellation circuits having multiport transformers," U.S. Patent 9 577 683, Feb. 21, 2017.

- [38] B. van Liempd *et al.*, "A +70-dBm IIP3 electrical-balance duplexer for highly integrated tunable front-ends," *IEEE Trans. Microw. Theory Techn.*, vol. 64, no. 12, pp. 4274–4286, Dec. 2016.

- [39] M. Mikhemar, H. Darabi, and A. Abidi, "A tunable integrated duplexer with 50 dB isolation in 40 nm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2009, pp. 386–387.

- [40] S. H. Abdelhalem, P. S. Gudem, and L. E. Larson, "Hybrid transformer-based tunable differential duplexer in a 90-nm CMOS process," *IEEE Trans. Microw. Theory Techn.*, vol. 61, no. 3, pp. 1316–1326, Mar. 2013.

- [41] B. van Liempd, A. Visweswaran, S. Ariumi, S. Hitomi, P. Wambacq, and J. Craninckx, "Adaptive RF front-ends using electrical-balance duplexers and tuned saw resonators," *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 11, pp. 4621–4628, Nov. 2017.

- [42] B. Hershberg, B. van Liempd, X. Zhang, P. Wambacq, and J. Craninckx, "A dual-frequency 0.7-to-1 GHz balance network for electrical balance Duplexers," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Jan./Feb. 2016, pp. 356–357.

- [43] B. van Liempd, B. Hershberg, B. Debaillie, P. Wambacq, and J. Craninckx, "An electrical-balance Duplexer for in-band full-duplex with -85 dBm in-band distortion at +10 dBm TX-power," in *Proc. 41st Eur. Solid-State Circuits Conf. (ESSCIRC)*, Sep. 2015, pp. 176–179.

- [44] B. van Liempd et al., "A +70 dBm IIP3 single-ended electrical-balance Duplexer in 0.18 μm SOI CMOS," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2015, pp. 1–3.

- [45] B. van Liempd, J. Craninckx, R. Singh, P. Reynaert, S. Malotaux, and J. R. Long, "A dual-notch +27 dBm Tx-power electrical-balance Duplexer," in *Proc. 40th Eur. Solid State Circuits Conf. (ESSCIRC)*, Sep. 2014, pp. 463–466.

- [46] E. Kargaran, S. Tijani, G. Pini, D. Manstretta, and R. Castello, "Low power wideband receiver with RF self-interference cancellation for fullduplex and FDD wireless diversity," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2017, pp. 348–351.

- [47] M. Ramella, I. Fabiano, D. Manstretta, and R. Castello, "A 1.7–2.1 GHz +23 dBm TX power compatible blocker tolerant FDD receiver with integrated duplexer in 28 nm CMOS," in *Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC)*, Nov. 2015, pp. 1–4.

- [48] J. Zhou, P. R. Kinget, and H. Krishnaswamy, "A blocker-resilient wideband receiver with low-noise active two-port cancellation of >0 dBm TX leakage and TX noise in RX band for FDD Co-existence," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2014, pp. 352–353.

- [49] D. J. van den Broek, E. A. M. Klumperink, and B. Nauta, "A self-interference-cancelling receiver for in-band full-duplex wireless with low distortion under cancellation of strong TX leakage," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2015, pp. 1–3.

- [50] L. Calderin, S. Ramakrishnan, A. Puglielli, E. Alon, B. Nikolić, and A. M. Niknejad, "Analysis and design of integrated active cancellation transceiver for frequency division duplex systems," *IEEE J. Solid-State Circuits*, vol. 52, no. 8, pp. 2038–2054, Aug. 2017.

- [51] S. Ramakrishnan, L. Calderin, A. Puglielli, E. Alon, A. Niknejad, and B. Nikolić, "A 65 nm CMOS transceiver with integrated active cancellation supporting FDD from 1 GHz to 1.8 GHz at +12.6 dBm TX power leakage," in *Proc. IEEE Symp. VLSI Circuits (VLSI-Circuits)*, Jun. 2016, pp. 1–2.

- [52] D. J. van den Broek, E. A. M. Klumperink, and B. Nauta, "A self-interference cancelling front-end for in-band full-duplex wireless and its phase noise performance," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, May 2015, pp. 75–78.

- [53] A. El Sayed et al., "A full-duplex receiver with 80 MHz bandwidth self-interference cancellation circuit using baseband Hilbert transform equalization," in Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC), Jun. 2017, pp. 360–363.

- [54] A. Medra et al., "An 80 GHz low-noise amplifier resilient to the TX spillover in phase-modulated continuous-wave radars," *IEEE J. Solid-State Circuits*, vol. 51, no. 5, pp. 1141–1153, May 2016.

- [55] S. A. Ayati, D. Mandal, B. Bakkaloglu, and S. Kiaei, "Adaptive integrated CMOS circulator," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, May 2016, pp. 146–149.

- [56] N. Reiskarimian and H. Krishnaswamy, "Magnetic-free non-reciprocity based on staggered commutation," *Nature Commun.*, vol. 7, Apr. 2016, Art. no. 11217.

- [57] N. Reiskarimian, J. Zhou, and H. Krishnaswamy, "A CMOS passive LPTV nonmagnetic circulator and its application in a full-duplex receiver," *IEEE J. Solid-State Circuits*, vol. 52, no. 5, pp. 1358–1372, May 2017.

- [58] B. Ř. Hallford, "Investigation of a single-sideband mixer anomaly," *IEEE Trans. Microw. Theory Techn.*, vol. MTT-31, no. 12, pp. 1030–1038, Dec. 1983

- [59] J. A. Weldon et al., "A 1.75 GHz highly-integrated narrow-band CMOS transmitter with harmonic-rejection mixers," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2001, pp. 160–161.

- [60] C. Huang, Y. Chen, T. Zhang, V. Sathe, and J. C. Rudell, "A 40 nm CMOS single-ended switch-capacitor harmonic-rejection power amplifier for ZigBee applications," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, May 2016, pp. 214–217.

[61] E. Mammei *et al.*, "Analysis and design of a power-scalable continuous-

- [61] E. Mammei et al., "Analysis and design of a power-scalable continuoustime FIR equalizer for 10 Gb/s to 25 Gb/s multi-mode fiber EDC in 28 nm LP CMOS," *IEEE J. Solid-State Circuits*, vol. 49, no. 12, pp. 3130–3140, Dec. 2014.

- [62] A. Gholian, Y. Ma, and Y. Hua, "A numerical investigation of all-analog radio self-interference cancellation," in *Proc. IEEE 15th Int. Workshop Signal Process. Adv. Wireless Commun. (SPAWC)*, Jun. 2014, pp. 459–463.

- pp. 459–463.

[63] T. Zhang, Y. Chen, C. Huang, and J. C. Rudell, "A low-noise reconfigurable full-duplex front-end with self-interference cancellation and harmonic-rejection power amplifier for low power radio applications," in *Proc. 43rd Eur. Solid-State Circuits Conf. (ESSCIRC)*, Sep. 2017, pp. 336–339.

- [64] B. G. Perumana, J.-H. C. Zhan, S. S. Taylor, B. R. Carlton, and J. Laskar, "Resistive-feedback CMOS low-noise amplifiers for multiband applications," *IEEE Trans. Microw. Theory Techn.*, vol. 56, no. 5, pp. 1218–1225, May 2008.

[65] D. Im, H.-T. Kim, and K. Lee, "A CMOS resistive feedback differential

- [65] D. Im, H.-T. Kim, and K. Lee, "A CMOS resistive feedback differential low-noise amplifier with enhanced loop gain for digital TV tuner applications," *IEEE Trans. Microw. Theory Techn.*, vol. 57, no. 11, pp. 2633–2642, Nov. 2009.

[66] H. Hedayati, W.-F. A. Lau, N. Kim, V. Aparin, and K. Entesari,

- [66] H. Hedayati, W.-F. A. Lau, N. Kim, V. Aparin, and K. Entesari, "A 1.8 dB NF blocker-filtering noise-canceling wideband receiver with shared TIA in 40 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 50, no. 5, pp. 1148–1164, May 2015.

- [67] S. K. Garakoui, E. A. M. Klumperink, B. Nauta, and F. E. van Vliet, "Compact cascadable g<sub>m</sub>-C all-pass true time delay cell with reduced delay variation over frequency," *IEEE J. Solid-State Circuits*, vol. 50, no. 3, pp. 693–703, Mar. 2015.

- [68] S. K. Garakoui, E. A. M. Klumperink, B. Nauta, and F. E. van Vliet, "A 1-to-2.5 GHz phased-array IC based on g<sub>m</sub>-RC all-pass time-delay cells," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2012, pp. 80–82.

- [69] S. K. Garakoui, E. A. M. Klumperink, B. Nauta, and F. E. van Vliet, "Frequency limitations of first-order g<sub>m</sub>-RC all-pass delay circuits," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 60, no. 9, pp. 572–576, Sep. 2013.

- [70] F. Bruccoleri, E. A. M. Klumperink, and B. Nauta, "Wide-band CMOS low-noise amplifier exploiting thermal noise canceling," *IEEE J. Solid-State Circuits*, vol. 39, no. 2, pp. 275–282, Feb. 2004.

[71] F. Bruccoleri, E. A. M. Klumperink, and B. Nauta, "Noise can-

- [71] F. Bruccoleri, E. A. M. Klumperink, and B. Nauta, "Noise cancelling in wideband CMOS LNAs," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, vol. 1. Feb. 2002, pp. 406–407.

- [72] A. Afsahi, A. Behzad, and L. E. Larson, "A 65 nm CMOS 2.4 GHz 31.5 dBm power amplifier with a distributed LC power-combining network and improved linearization for WLAN applications," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2010, pp. 452–453.

- [73] A. Afsahi, A. Behzad, V. Magoon, and L. E. Larson, "Linearized dual-band power amplifiers with integrated baluns in 65 nm CMOS for a 2×2 802.11n MIMO WLAN SoC," *IEEE J. Solid-State Circuits*, vol. 45, no. 5, pp. 955–966, May 2010.

- [74] I. Fabiano, M. Sosio, A. Liscidini, and R. Castello, "SAW-less analog front-end receivers for TDD and FDD," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3067–3079, Dec. 2013.

- vol. 48, no. 12, pp. 3067–3079, Dec. 2013.

[75] I. Lee, D. Sylvester, and D. Blaauw, "A constant energy-per-cycle ring oscillator over a wide frequency range for wireless sensor nodes," *IEEE J. Solid-State Circuits*, vol. 51, no. 3, pp. 697–711, Mar. 2016.

[76] A. Mostajeran, M. S. Bakhtiar, and E. Afshari, "A 2.4 GHz VCO with

- [76] A. Mostajeran, M. S. Bakhtiar, and E. Afshari, "A 2.4 GHz VCO with FOM of 190 dBc/Hz at 10 kHz-to-2 MHz offset frequencies in 0.13 μm CMOS using an ISF manipulation technique," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2015, pp. 1–3.

**Tong Zhang** (S'17–M'18) received the B.S. degree in electrical engineering from Southeast University, Nanjing, China, in 2011, and the M.S. and Ph.D. degrees in electrical engineering from the University of Washington, Seattle, WA, USA, in 2014 and 2017, respectively.

From 2013 to 2014, he was an Intern with Qualcomm Inc., San Jose, CA, USA, and with Google Inc., Mountain View, CA, USA, in 2015, where he was involved in various projects such as millimeterwave (mm-wave) front-end circuits and baseband

analog circuits for different applications. He is currently a Hardware Engineer with Verily Life Sciences, South San Francisco, CA, USA (formerly Google Life Sciences). His current research interests include developing transmitter self-interference mitigation (SIM) techniques for FDD/in-band full-duplex radios, providing high-speed point-to-point communication at mm-wave frequencies, and developing next-generation medical devices using state-of-the-art technologies.

Dr. Zhang was a recipient of the Analog Device Outstanding Student Designer Award (2014–2015), the SSCS Predoctoral Achievement Award (2015–2016), the UW EE Yang Award for Outstanding Doctoral Student (2017), the UW Graduate School Distinguished Dissertation Award (2017), and the ISSCC Student Travel Grant Award (2017).

Chenxin Su (S'15) received the B.S. degree in electrical engineering from the Nanjing University of Aeronautics and Astronautics, Nanjing, China, in 2008, and the M.S. degree in electrical engineering from Ohio State University, Columbus, OH, USA, in 2011. He is currently pursuing the Ph.D. degree with the University of Washington, Seattle, WA, USA.

Ali Najafi (S'15) received the B.Sc. and M.Sc. degrees in electrical engineering from the Sharif University of Technology, Tehran, Iran, in 2011 and 2013, respectively. He is currently pursuing the Ph.D. degree in electrical engineering with the University of Washington, Seattle, WA, USA

He was an Intern with Qualcomm Inc., San Diego, CA, USA, in 2016, and Apple Inc., Cupertino, CA, USA, in 2017. His current research interests include low-power wireless communication networks and

systems and integrated circuit design for low-power radios.

Jacques Christophe Rudell (M'00–SM'09) received the B.S. degree in electrical engineering from the University of Michigan, Ann Arbor, MI, USA, and the M.S. and Ph.D. degrees in electrical engineering from the University of California at Berkeley, Berkeley, CA, USA.

He was an RF IC Designer with Qualcomm Inc., San Diego, CA, USA, and Intel Corporation, Hillsboro, OR, USA. In 2009, he joined the University of Washington, Seattle, WA, USA, where he is currently an Associate Professor

of electrical engineering. His current research interests include RF and millimeter-wave integrated circuit designs for communication systems, in addition to biomedical electronics for imaging and neural interface applications.

Dr. Rudell is an Active Member at the Center for Sensorimotor Neural Engineering (CSNE), and an NSF Engineering Research Center (ERC) based at the University of Washington. He is the Co-Director of the Center for Design of Analog-Digital Integrated Circuits (CDADIC). He was a recipient of the Demetri Angelakos Memorial Achievement Award, a citation given to one student per year by the EECS Department, the 2008 ISSCC Best Evening Session Award, and the 2015 NSF Career Award. He was a co-recipient of the best paper awards at the International Solid-State Circuits Conference (twice), namely, the 1998 Jack Kilby Award and the 2001 Lewis Winner Award, and the 2011 and 2014 RFIC Symposium Best Student Paper Award. He served on the ISSCC Technical Program Committee (2003–2010), and the MTT-IMS Radio Frequency Integrated Circuits (RFIC) Symposium Steering Committee (2002–2013), where he was the 2013 General Chair. He currently serves on the Technical Program Committee of ESSCIRC. He was an Associate Editor of the *Journal of Solid-State Circuits* (2009–2015).